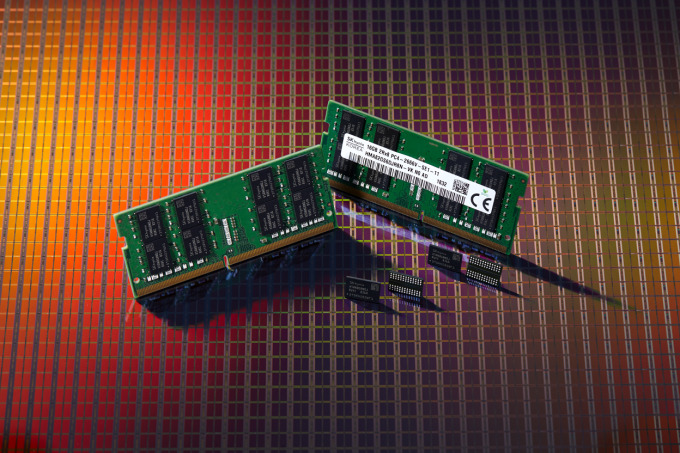

[서울=뉴스핌] 양태훈 기자 = 세계 D램 2위 업체 SK하이닉스가 10나노미터(nm, 10억분의 미터) 중반의 미세공정 기술을 기반으로 한 'DDR4 D램' 개발에 성공했다. 경기 이천에 위치한 반도체공장(M14 등)에서 내년 1분기부터 PC·서버·모바일 등용 제품을 양산한다.

12일 SK하이닉스는 10nm 중반 미세공정 기반의 DDR4 D램(용량 8기가비트) 개발에 성공, 본격적인 양산에 돌입한다고 밝혔다. 10nm 중반 미세공정 진입은 삼성전자(시장 1위)와 마이크론(시장 3위) 대비 늦었지만, 실제 양산물량에 있어서는 마이크론을 앞서나갈 것으로 업계는 보고 있다.

반도체 업계 관계자는 "10nm 중반 미세공정 기술 개발의 완료시점은 삼성전자, 마이크론보다 늦었지만, 실제 양산에 있어서는 마이크론보다 우위를 보일 것"이라며 "10nm 중반 미세공정 기반의 제품들이 본격적으로 양산되는 시점은 내년부터다"라고 설명했다.

10nm 중반 미세공정 기술은 기존 10nm 후반 미세공정 대비 20% 향상된 생산성과 15% 높아진 전력효율을 제공하는 것이 특징이다. 데이터 전송 속도도 DDR4 규격이 지원하는 최고 속도인 3200메가비피에스(Mbps)를 구현해 더욱 빨라졌다.

SK하이닉스는 데이터 전송 속도의 향상을 위해 10nm 중반 미세공정에 '4페이즈 클록킹(4Phase Clocking)' 설계 기술을 적용했다. 이는 데이터 전송 시 주고받는 신호를 기존대비 두 배로 늘려 제품의 동작 속도와 안정성을 향상시켜준다. 고속도로 톨게이트의 요금 정산소를 늘려 차량의 통행을 원활히 하는 것과 같은 개념이다.

10nm 중반 미세공정에는 향상된 전력효율 만큼 데이터 오류발생 가능성을 줄이기 위한 독자적인 제어 기술 '센스 앰프(Sense Amp)'도 도입됐다. 이는 D램 셀(데이터 저장 공간)에 작은 전하 형태로 저장되는 데이터를 감지하고, 이를 증폭시켜 외부로 전달하는 성능 전반을 강화한 기술이다.

공정이 미세화 될수록 트랜지스터(신호 및 전력을 증폭하는 스위치)의 크기가 줄어들어 데이터 감지 오류 발생 가능성이 높아지는 만큼 트랜지스터의 구조를 개선해 오류 발생 가능성을 최소화 한 것이다.

김석 SK하이닉스 D램 마케팅담당 상무는 "이번에 개발 완료된 10나노급(10nm 중반) DDR4는 고객이 요구하는 성능과 용량을 모두 갖춘 제품"이라며 "내년 1분기부터 공급에 나서 시장 수요에 적극 대응 할 것"이라고 강조했다.

한편, SK하이닉스는 지난 2005년 90nm급 미세공정 기반의 D램 양산을 시작한 후, 2012년 20nm 후반의 미세공정을, 2013년 20nm 중반의 미세공정을, 2015년 20nm 초반의 미세공정을, 2017년 10nm 후반의 미세공정 기술을 개발해 D램 양산을 전개해왔다.

올해 3분기에는 D램 시장호황에 힘입어 매출 11조4168억원, 영업이익 6조4725억원의 분기 사상 최대 실적을 기록했다.

flame@newspim.com

영상

영상