[서울=뉴스핌] 서영욱 기자 = 글로벌 반도체 기업들의 기술 경쟁이 '점입가경'이다.

세계 파운드리(반도체 위탁생산) 1위 기업인 TSMC는 3나노미터(㎚=10억분의 1m) 반도체 양산을 위한 설비 구축에 들어갔다. 2나노 반도체 양산을 위한 공장 부지까지 확보한 상태다. 인텔은 오는 2025년까지 2나노 반도체 개발을 위한 로드맵을 세웠다. 가장 먼저 2나노 반도체를 생산해 선두 탈환을 노린다.

삼성전자도 내년말 3나노 반도체 양산을 목표로 기술 개발이 한창이다. 다만 아직까지 2나노 공정 도입에 관한 언급은 없다. 삼성은 신기술인 'GAA(Gate All Around)' 기반의 3나노 반도체를 가장 먼저 도입해 기술 격차를 뒤집겠다는 전략이다.

◆TSMC, 3나노 반도체 장비 설치하며 '속도전'

6일 반도체업계에 따르면 TSMC는 최근 대만 타이난시에 있는 공장(팹18)에 3나노 반도체 생산이 가능한 설비 증축에 나섰다.

대만 현지 언론에 따르면 팹18은 TSMC가 5나노 반도체를 양산하고 있는 공장이다. 현지 언론에 따르면 팹18의 8개 라인 중 4개 라인은 5나노 반도체를, 나머지 4개 라인은 3나노 반도체를 생산할 전망이다.

TSMC는 애플을 비롯해 퀄컴, 엔비디아 등을 주요고객을 확보한 것으로 알려졌다. 이들과 함께 3나노 제품 테스트를 시작해 내년 하반기 양산이 유력하다.

TSMC는 3나노에 이어 2나노 공정 개발에도 속도를 내고 있다. 대만 정부는 지난달 28일 TSMC가 제출한 2나노 반도체 공장 신설 계획을 승인했다. 대만 북부 신주산업단지에 50에이커 규모로, 내년 초 착공 예정이다. 오는 2023년이면 생산 장비를 설치할 수 있을 전망이다.

업계에선 TSMC가 오는 2024년이면 2나노 반도체를 생산할 수 있을 것으로 보고 있다. TSMC는 미국 애리조나주에도 2나노 공정이 적용된 차세대 반도체 공장 건립을 검토하고 있는 것으로 알려졌다.

◆"삼성·TSMC 잡자" 인텔의 매서운 추격

뒤늦게 파운드리 시장에 뛰어든 인텔의 기세도 무섭다. 인텔은 지난달 27일 열린 온라인 기술전략 설명회에서 오는 2025년까지 파운드리 사업 확장 로드맵을 발표했다. 4년 내 TSMC와 삼성을 따라잡겠다는 포부다.

특히 인텔의 공격적인 투자와 기술개발에 대한 의지는 경쟁사인 TSMC와 삼성을 긴장시켰다. 인텔은 내년 4나노급(인텔4)에 진입해 2023년 3나노급(인텔3) 반도체를 생산하겠다는 계획이다. 2024년에는 2나노급(인텔20A)을 생산, 2025년부터 본격 양산한다는 전략이다.

◆2나노 언급없는 삼성..GAA 도입해 기술경쟁력 확보

반도체 공정에서 말하는 '나노미터'는 반도체 안 전기 회로의 선폭을 의미한다. 숫자가 작을수록 전기 회로가 미세해진다. 선폭이 줄어들면 더 많은 전기 회로를 집어넣을 수 있어 반도체 성능은 올라간다. 또 칩 크기가 작아지면서 웨이퍼 당 생산량이 증가해 원가 경쟁력을 강화할 수 있다. 반도체 기업들이 초미세공정 경쟁에 나서는 이유다. 초미세공정의 선두를 달리고 있는 삼성전자와 TSMC는 현재 5나노 반도체를 양산하고 있다.

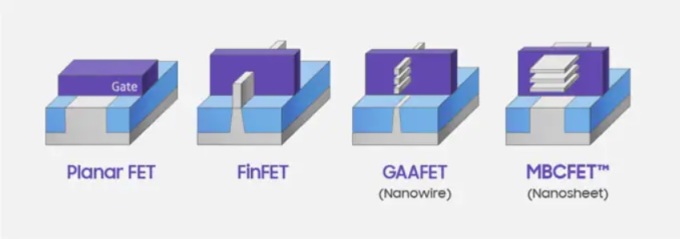

삼성전자는 반도체 선폭을 줄이는 경쟁에서 벗어나 반도체 구조 자체에 혁신을 가져다 줄 수 있는 신기술을 확보해 반전을 꾀하고 있다. 삼성의 무기는 GAA다. GAA는 기존 핀펫의 3차원 구조에 채널 아랫면까지 모두 감싸 전류의 흐름을 세밀하게 제어하는 기술이다. 여기에 삼성은 한 발 더 나아가 MBCFET(Multi Bridge Channel FET)을 독자적으로 개발했다. 기존의 가늘고 긴 와이어 형태의 GAA 구조를 한층 더 발전시켜 종이처럼 얇고 긴 모양의 나노시트를 적층하는 방식이다.

MBCFET공정은 기존 7나노 핀 트랜지스터 공정과 비교했을 때 소비전력이 약 50% 절감되고 성능은 30% 정도 개선되며 공간도 약 45%나 줄일 수 있다.

최시영 삼성전자 파운드리 사장은 지난 6월 열린 VLSI 심포지엄에서 "핀펫이 모바일 시스템온칩(SoC) 시대를 열었던 것처럼 MBCFET은 고성능·저전력 컴퓨팅, AI, 5G 확산 가속화를 통해 '데이터 기반 사회'를 열 것으로 기대한다"며 "삼성의 파운드리 비전은 기술 경쟁력을 기반으로 고객들에게 공정 및 설계 유연성을 제공하는 것이며 어떤 도전에도 대응할 준비가 돼 있다"고 말했다.

삼성은 GAA 기술을 적용한 1세대 3나노 반도체를 내년, 2세대 반도체를 오는 2023년 양산할 계획이다. 삼상전자는 지난달 29일 오전 열린 2분기 실적발표 컨퍼런스콜에서 "3나노 GAA 1세대 공정은 주요 고객사와 제품 설계를 진행 중"이라며 "GAA 1세대와 2세대 양산을 통해 파운드리 시장에서 삼성의 리더십을 더욱 확대할 수 있을 것으로 기대한다"고 전했다.

syu@newspim.com

영상

영상